# DSC2110FL2-A0026

#### Crystal-less<sup>™</sup> Configurable Clock Generator

#### **General Description**

The DSC2110FL2-A0026 is a programmable, high performance LVCMOS oscillators utilizing Micrel's proven silicon MEMS technology to provide excellent jitter and stability while incorporating additional device functionality.

The DSC2110FL2-A0026 allows the user to easily modify the frequency using I2C interface. The user can also select from two pre-programmed default output frequencies using the frequency select pin.

### Applications

- Consumer Electronics

- Storage Area Networks

- SATA, SAS, Fibre Channel

- Passive Optical Networks

EPON, 10G-EPON, GPON, 10G-GPON

- Ethernet

- 1G, 10GBASE-T/KR/LR/SR, and FCoE

- HD/SD/SDI Video & Surveillance

- PCI Express

- Automotive

#### Features

- Frequency and output formats:

- LVCMOS

- 75/25MHz

- Low RMS phase jitter: <1ps (typ)

- ±25ppm frequency stability

- $\bullet$  -40°C to +105°C ext. industrial temperature range

- High supply noise rejection: -50dBc

- I2C programmable frequency and drive

- Excellent shock & vibration immunity - Qualified to MIL-STD-883

- High reliability

- 20x better MTF than quartz oscillators

- Supply range of 2.25 to 3.6V

- AEC-Q100 automotive qualified

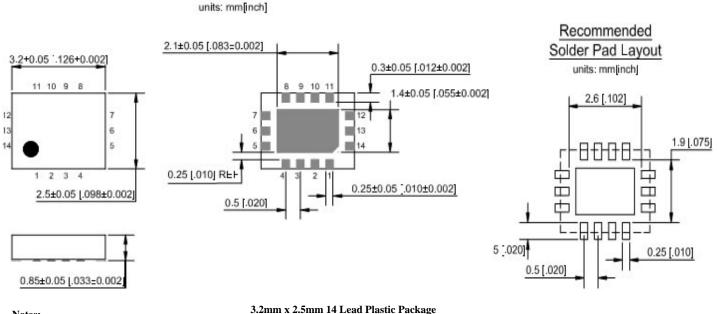

- 14-pin 3.2mm x 2.5mm QFN package

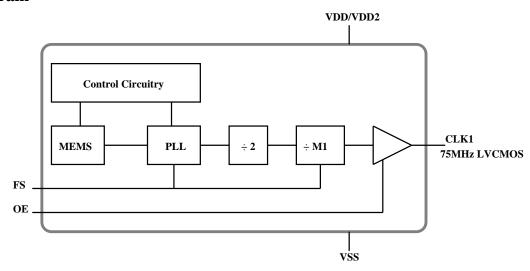

### **Block Diagram**

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

## **Ordering Information**

| Ordering Part Number | Industrial Temperature Range | Shipping      | Package                  |

|----------------------|------------------------------|---------------|--------------------------|

| DSC2110FL2-A0026     | -40°C to +105°C              | Tube          | 14-pin 3.2mm x 2.5mm QFN |

| DSC2110FL2-A0026T    | -40°C to +105°C              | Tape and Reel | 14-pin 3.2mm x 2.5mm QFN |

Devices are Green and RoHS compliant. Sample material may have only a partial top mark.

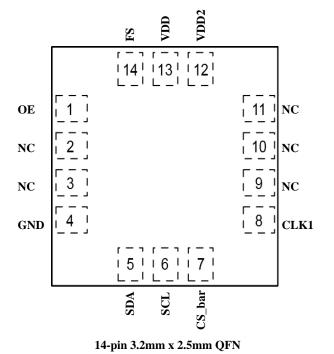

### **Pin Configuration**

### **Pin Description**

| Pin Number | Pin Name  | Pin Type | Pin Function                                            |

|------------|-----------|----------|---------------------------------------------------------|

| 1          | OE        | Ι        | Enables outputs when high and disables outputs when low |

| 2          | NC        |          | Leave unconnected or connect to ground                  |

| 3          | NC        |          | Leave unconnected or connect to ground                  |

| 4          | GND       | PWR      | Ground                                                  |

| 5          | SDA       | Ι        | I2C serial data                                         |

| 6          | SCL       | Ι        | I2C serial clock                                        |

| 7          | CS_bar    |          | I2C chip select (active low)                            |

| 8          | CLK1      | 0        | LVCMOS output                                           |

| 9          | NC        |          | Leave unconnected or connect to ground                  |

| 10         | NC        |          | Leave unconnected or connect to ground                  |

| 11         | NC        |          | Leave unconnected or connect to ground                  |

| 12, 13     | VDD2, VDD | PWR      | Power supply                                            |

| 14         | FS        | Ι        | Frequency select pin, see Table 2 for details           |

The DSC2110FL2-A0026 is a LVCMOS oscillator consisting of a MEMS resonator and a supporting PLL IC. The LVCMOS output is generated through independent 8-bit programmable dividers from the output of the internal PLL.

DSC2110FL2-A0026 allows for easy programming of the output frequencies using I2C interface. Upon power-up, the initial output frequency is controlled by an internal pre-programmed memory (OTP). This memory stores all coefficients required by the PLL for two different default frequencies. The control pin (FS) selects the initial frequency. Once the device is powered up, a new output frequency can be programmed. Programming details are provided in the Programming Guide. When OE (pin 1) is floated or connected to VDD, the DSC2110FL2-A0026 is in operational mode. Driving OE to ground will disable both output drivers (hi-impedance mode).

DSC2110FL2-A0026 has programmable output drive strength, which can be controlled via I2C.

Table 1 displays typical rise / fall times for the output with a 15pF load capacitance as a function of these control bits at VDD = 3.3V and room temperature.

|         | Output Drive Strength Bits [OS2, OS1, OS0] - Default is [111] |     |     |     |     |     |     |     |

|---------|---------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

|         | 000                                                           | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

| tr (ns) | 2.1                                                           | 1.7 | 1.6 | 1.4 | 1.3 | 1.3 | 1.2 | 1.1 |

| tf (ns) | 2.5                                                           | 2.4 | 2.4 | 2   | 1.8 | 1.6 | 1.3 | 1.3 |

Table 1. Rise/Fall Times for Drive Strengths

### **Output Clock Frequencies**

Frequency select bits are weakly tied high so if left unconnected the default setting will be [1] and the device will output the associated frequency highlighted in bold.

| Freq (MHz) | Freq Select Bit [FS] - Default is [1] |    |  |

|------------|---------------------------------------|----|--|

|            | 0                                     | 1  |  |

| CLK1       | 25                                    | 75 |  |

Table 2. Pin-Selectable Output Frequencies

### **Absolute Maximum Ratings**

| Item                    | Min. | Max.                | Units | Condition  |

|-------------------------|------|---------------------|-------|------------|

| Supply Voltage          | -0.3 | +4.0                | V     |            |

| Input Voltage           | -0.3 | VDD + 0.3           | V     |            |

| Junction Temp           | -    | +150                | °C    |            |

| Storage Temp            | -55  | +150                | °C    |            |

| Soldering Temp          | -    | +260                | °C    | 40sec max. |

| ESD<br>HBM<br>MM<br>CDM | -    | 4000<br>400<br>1500 | V     |            |

1000+ years of data retention on internal memory

| Parameter                                                     | Symbol     | Condition                                                                             | Min.            | Тур.               | Max.           | Units |

|---------------------------------------------------------------|------------|---------------------------------------------------------------------------------------|-----------------|--------------------|----------------|-------|

| Supply Voltage <sup>1</sup>                                   | VDD        |                                                                                       | 2.25            |                    | 3.6            | v     |

| Supply Current                                                | IDD        | OE pin low - output is disabled                                                       |                 | 21                 | 23             | mA    |

| Frequency Stability                                           | ∆F         | Includes frequency variation due to initial tolerance, temp. and power supply voltage |                 |                    | ±25            | ppm   |

| Aging                                                         | ΔF         | First year (@ 25°C)                                                                   |                 |                    | ±5             | ppm   |

| Startup Time <sup>2</sup>                                     | tSU        | $T = 25^{\circ}C$                                                                     |                 |                    | 5              | ms    |

| Input Logic Levels<br>Input Logic High<br>Input Logic Low     | VIH<br>VIL |                                                                                       | 0.75 x VDD<br>- |                    | 0.25 x VDD     | v     |

| Output Disable Time <sup>3</sup>                              | tDA        |                                                                                       |                 |                    | 5              | ns    |

| Output Enable Time <sup>3</sup>                               | tEN        |                                                                                       |                 |                    | 20             | ns    |

| Pull-Up Resistor <sup>4</sup>                                 |            | Pull-up exists on all digital IO                                                      |                 | 40                 |                | kOhms |

|                                                               | •          | LVCMOS Output                                                                         |                 |                    |                |       |

| Supply Current <sup>4</sup>                                   | IDD        | OE pin high - output is enabled<br>CL = 15pF, F0 = 125MHz                             |                 | 31                 | 35             | mA    |

| Output Logic Levels<br>Output Logic High<br>Output Logic Low  | VOH<br>VOL | $I = \pm 6mA$                                                                         | 0.9 x VDD<br>-  |                    | -<br>0.1 x VDD | v     |

| Output Transition Time <sup>3</sup><br>Rise Time<br>Fall Time | tR<br>tF   | 20% to 80%<br>CL = 15pF                                                               |                 | 1.1<br>1.3         | 2<br>2         | ns    |

| Frequency                                                     | CLK1       | [FS] = [1]                                                                            |                 | 75                 |                | MHz   |

| Output Duty Cycle                                             | SYM        |                                                                                       | 45              |                    | 55             | %     |

| Period Jitter                                                 | JPER       | F0 = 125MHz                                                                           |                 | 3                  |                | psRMS |

| Integrated Phase Noise                                        | JPH        | 200kHz to 20MHz @ 125MHz<br>100kHz to 20MHz @ 125MHz<br>12kHz to 20MHz @ 125MHz       |                 | 0.3<br>0.38<br>1.7 | 2              | psRMS |

#### **Specifications** (Unless specified otherwise: T = 25°C, max LVCMOS drive strength)

Notes:

1. Pin 12 VDD2, and pin 13 VDD should be filtered with 0.1uF capacitors.

$2.\ tSU$  is time to 100ppm stable output frequency after VDD is applied and outputs are enabled.

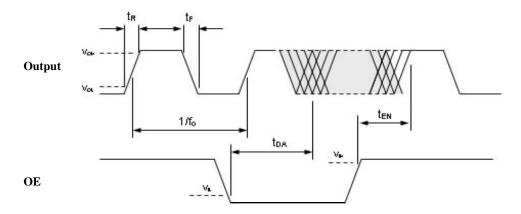

3. Output Waveform and Test Circuit figures below define the parameters.

4. Output is enabled if OE pin is floated or not connected.

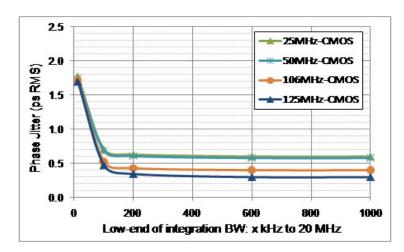

### **Nominal Performance Parameters** (Unless specified otherwise: T = 25°C, VDD = 3.3V)

Figure 1. LVCMOS Phase Jitter (integrated phase noise)

## **LVCMOS Output Waveform**

Figure 2. LVCMOS Output Waveform

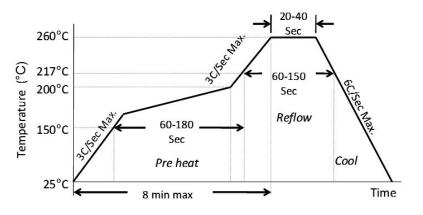

| MSL 1 @ 260°C refer to JSTD-020C  |              |  |  |  |

|-----------------------------------|--------------|--|--|--|

| Ramp-Up Rate (200°C to Peak Temp) | 3°C/sec Max. |  |  |  |

| Preheat Time 150°C to 200°C       | 60 - 180 sec |  |  |  |

| Time maintained above 217°C       | 60 - 150 sec |  |  |  |

| Peak Temperature                  | 255 - 260°C  |  |  |  |

| Time within 5°C of actual Peak    | 20 - 40 sec  |  |  |  |

| Ramp-Down Rate                    | 6°C/sec Max. |  |  |  |

| Time 25°C to Peak Temperature     | 8 min Max.   |  |  |  |

#### **Solder Reflow Profile**

Figure 3. Solder Reflow Profile

### **Package Information<sup>6</sup>**

#### Notes:

5. Connect the exposed die paddle to ground.

6. Package information is correct as of the publication date. For updates and most current information, go to www.micrel.com.

External Dimensions

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2015 Micrel, Incorporated.