AT43DK380 USB Host/Function **Development Kit**

**User Guide for Revision 1.0**

#### Table of Contents

| Section   | 1    |                                                      |     |

|-----------|------|------------------------------------------------------|-----|

| Introduct | tion |                                                      | 1-1 |

| 1.1       | De   | evelopment Kit Packages and Features                 | 1-1 |

| Section   | 2    |                                                      |     |

| Getting S | Star | ted                                                  | 2-1 |

| 2.1       |      | ectrostatic Warning                                  |     |

| 2.2       | Ur   | npacking the System                                  | 2-1 |

| 2.3       | -    | stem Requirements                                    |     |

| 2.4       |      | onnecting the Hardware                               |     |

| 2.5       |      | stalling AT43DK380 and Starting Up the USB Clinic    |     |

| 2.6       | 16   | esting the Hardware                                  | 2-3 |

| Section   |      |                                                      |     |

| Hardwar   |      | escription                                           |     |

| 3.1       | De   | escription of the Main Development Platform          |     |

| 3.        | 1.1  | AT43DK380 Processor Interface Connector              | 3-2 |

| 3.        | 1.2  | Jumper Settings                                      | 3-5 |

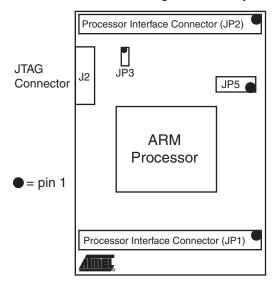

| 3.2       | ΑТ   | T43DC380-PDC1 Processor Daughter Card                | 3-7 |

| 3.5       | 2.1  | PDC1 Jumper Settings                                 | 3-7 |

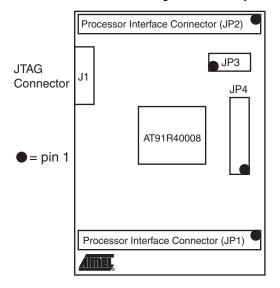

| 3.3       | ΑТ   | F43DC380-PDC2 Processor Daughter Card                | 3-8 |

| 3.        | 3.1  | PDC2 Jumper Settings                                 | 3-8 |

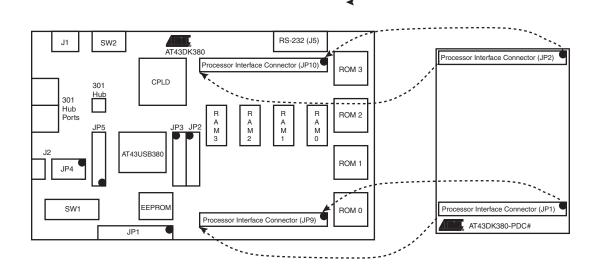

| 3.4       | ΑΊ   | T43DK380 Main Development Platform to PDC Connection | 3-9 |

| Section   | 4    |                                                      |     |

| USB Clir  | nic  |                                                      | 4-1 |

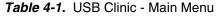

| 4.1       | Ма   | ain Menu                                             | 4-1 |

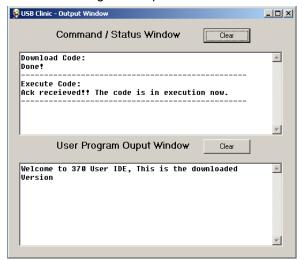

| 4.2       | Οι   | utput Window                                         | 4-2 |

| 4.:       | 2.1  | Command/Status Window                                | 4-2 |

| 4.5       | 2.2  | User Program Output Window                           | 4-2 |

| 4.3       | Co   | onnection                                            | 4-2 |

| 4.5       | 3.1  | Test Connectivity                                    | 4-3 |

| 4.5       | 3.2  | Check Device Enumerated                              | 4-3 |

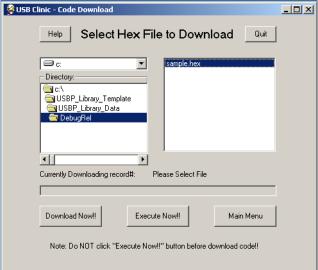

| 4.4       | Do   | ownload Code                                         | 4-3 |

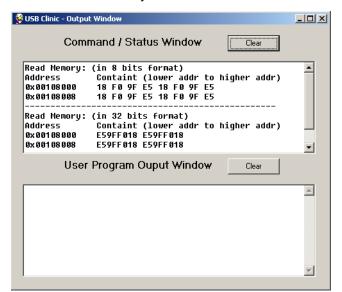

| 4.5       |      | emory                                                |     |

| 4.        | 5.1  | Fill Memory                                          | 4-5 |

| 4         | 5.2  | Read Memory                                          | 4-5 |

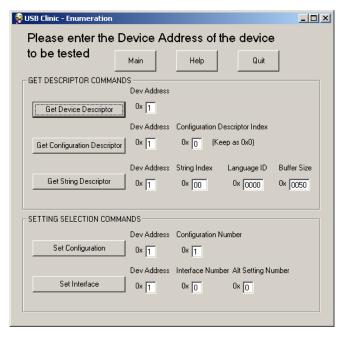

| 4.6 Enume                | eration                                                                    | 4-5  |

|--------------------------|----------------------------------------------------------------------------|------|

| 4.6.1 Ge                 | et Device Descriptor                                                       | 4-6  |

| 4.6.2 Ge                 | et Configuration Descriptor                                                | 4-6  |

| 4.6.3 Ge                 | et String Descriptor                                                       | 4-7  |

| 4.6.4 Se                 | et Configuration                                                           | 4-7  |

| 4.6.5 Se                 | et Interface                                                               | 4-7  |

| 4.7 Data T               | ransfer                                                                    | 4-8  |

| 4.7.1 Ge                 | et ISO Data                                                                | 4-8  |

| 4.7.2 Se                 | end ISO Data                                                               | 4-8  |

| 4.7.3 Ge                 | et Data                                                                    | 4-8  |

| 4.7.4 Se                 | end Data                                                                   | 4-8  |

| 4.7.5 Co                 | ontrol Transfer                                                            | 4-9  |

| 4.7.6 Cu                 | ustom Transfer                                                             | 4-9  |

| 4.8 Port Fe              | eatures                                                                    | 4-10 |

| 4.8.1 Se                 | et Port Feature                                                            | 4-10 |

| 4.8.2 Cle                | ear Port Feature                                                           | 4-10 |

| 4.9 Device               | State Control                                                              | 4-11 |

| 4.9.1 Re                 | eset Device                                                                | 4-11 |

| 4.9.2 Su                 | spend Device                                                               | 4-11 |

| 4.9.3 Re                 | esume Device                                                               | 4-11 |

| 4.10 Miscell             | laneous Notes                                                              | 4-11 |

| Section 5                |                                                                            |      |

| Building Firmwa          | are for the AT43DK380 Development Kit                                      | 5-1  |

| 5.1 Sample               | e Directory and File Structure                                             | 5-1  |

| 5.1.1 US                 | SBP ARM Project Guide                                                      | 5-2  |

| 5.1.2 "M                 | lake" Project                                                              | 5-4  |

| 5.2 ADS S                | Settings                                                                   | 5-5  |

| 5.3 Modify               | ring a Sample Application                                                  | 5-8  |

| Section 6 Generating Hex | r Files for Flash Mode in the AT43USB380 Developr                          | ment |

| Platform with Al         | DS                                                                         | 6-1  |

|                          | uction                                                                     |      |

| 6.2 Proced               | dure                                                                       | 6-1  |

| Section 7                |                                                                            | ·    |

| _                        | ween FLASH and ICE Mode and Download Mode                                  |      |

|                          | uction                                                                     |      |

|                          | rting to Flash Mode from ICE Mode                                          |      |

|                          | rting to Flash Mode from Download Moderting to Download Mode from ICE Mode |      |

| 7.4 001106               | any to bowined mode from the mode                                          |      |

| 7.5 Cor      | nverting to Download Mode from Flash Mode            | 7-4  |

|--------------|------------------------------------------------------|------|

| 7.6 Cor      | nverting to ICE Mode from Flash Mode                 | 7-4  |

| 7.7 Cor      | nverting to ICE Mode from Download Mode              | 7-4  |

| 7.8 Sun      | nmary                                                | 7-4  |

| Section 8    |                                                      |      |

| Technical Su | pport                                                | 8-1  |

| Section 9    |                                                      |      |

| Appendices   |                                                      | 9-1  |

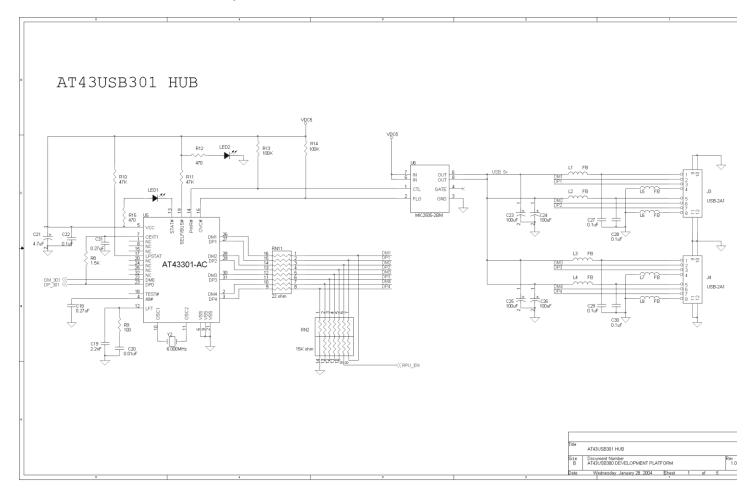

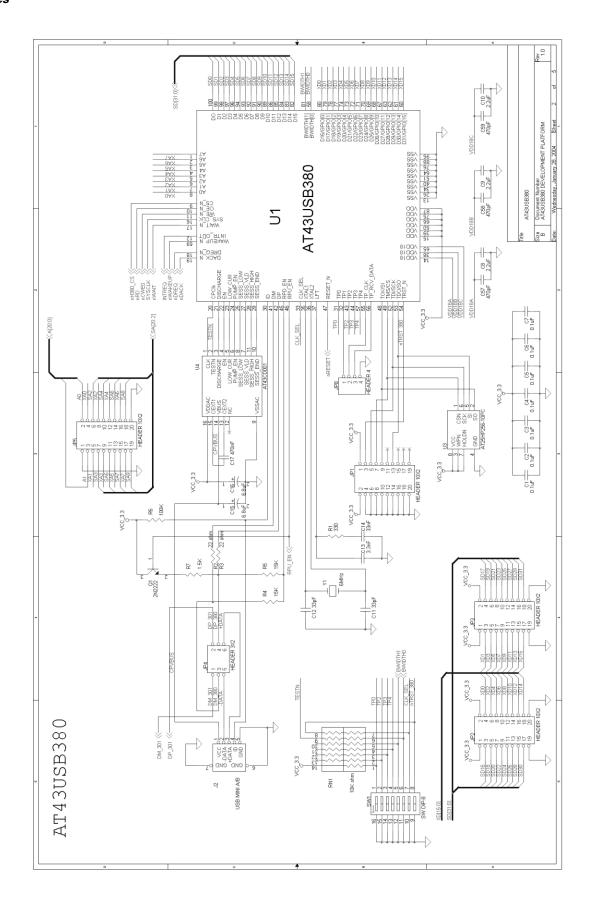

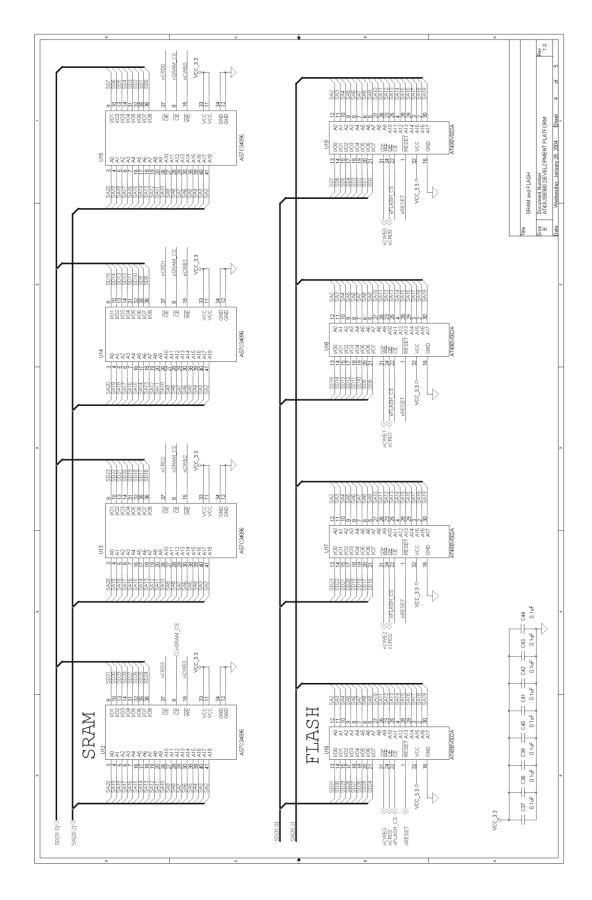

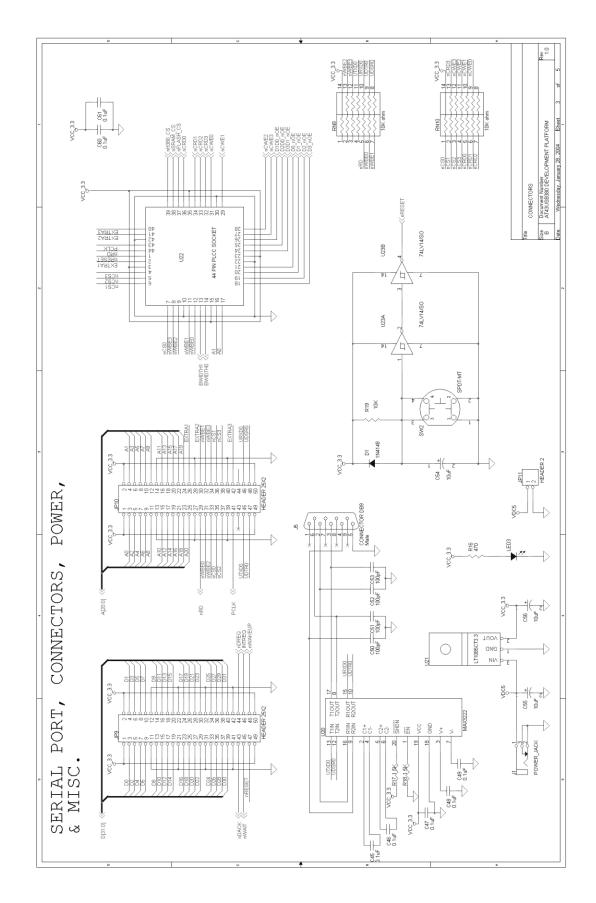

|              | 43DK380 Schematics                                   |      |

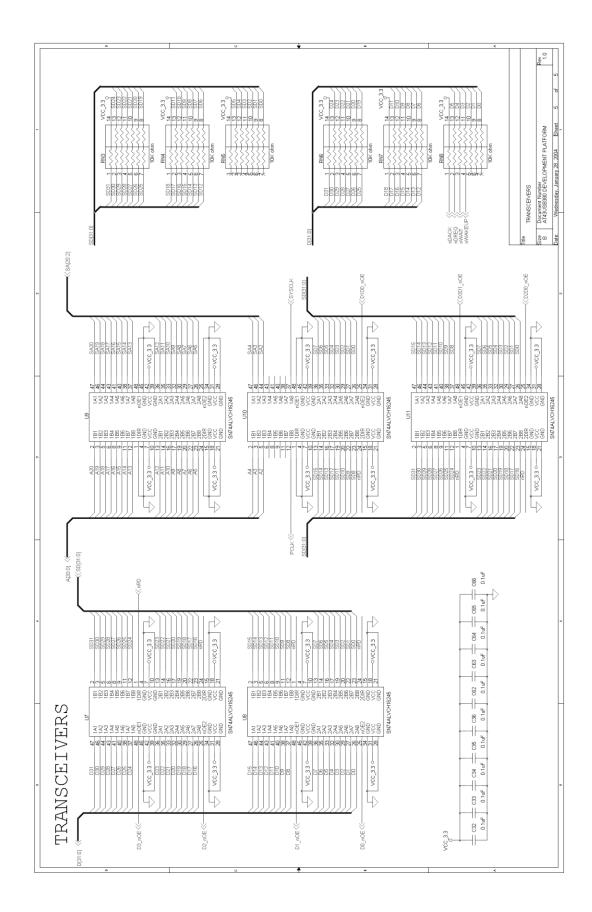

| 9.1.1        | AT43DK380 Main Development Platform Schematics       | 9-1  |

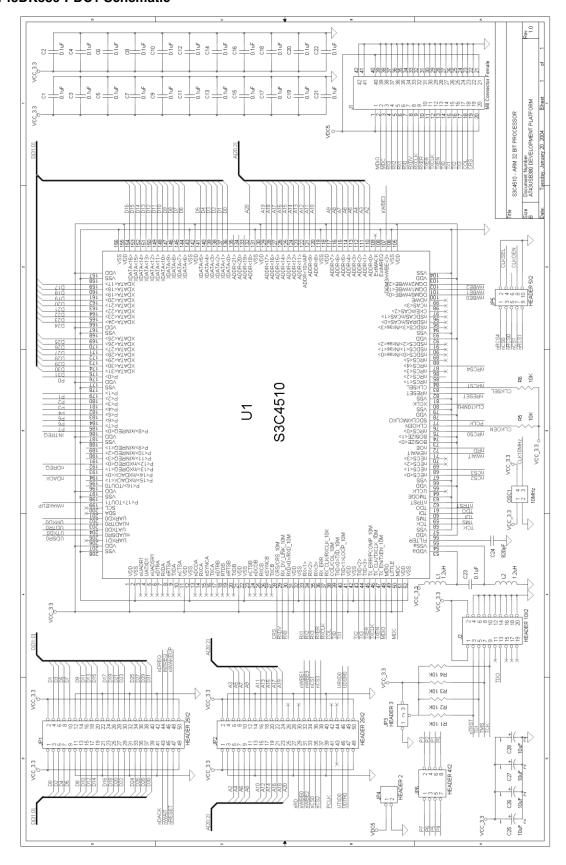

| 9.1.2        | AT43DK380-PDC1 Schematic                             | 9-6  |

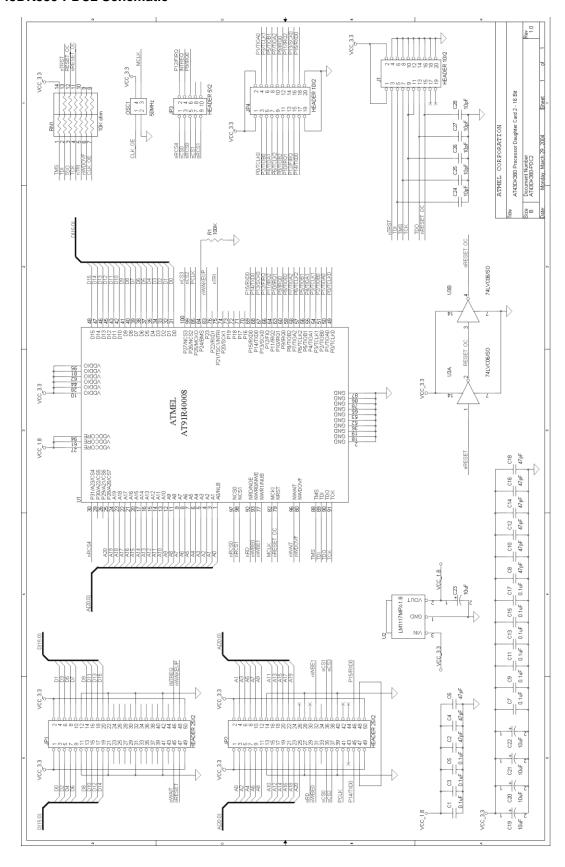

| 9.1.3        | AT43DK380-PDC2 Schematic                             | 9-7  |

| 9.2 AT4      | 43DK380 Bill of Materials (BOM)                      | 9-8  |

| 9.2.1        | AT43DK380 Main Development Platform BOM              | 9-8  |

| 9.2.2        | AT43DK380-PDC1 BOM                                   | 9-11 |

| 9.2.3        | AT43DK380-PDC2 BOM                                   | 9-12 |

| 0.2 AT/      | 13DK380 Main Dovolonment Platform CPLD VHDL Code Ref | 0_12 |

Table of Contents

### **Section 1**

### Introduction

Congratulations on your purchase of the AT43DK380 Development Kit. The AT43DK380 Main Development Platform is the AT43USB380 Host/Function/OTG Processor Development Platform to be used with a user target processor board or the AT43DK380 Processor Daughter Cards (PDCs). It is designed to allow real-time firmware development and evaluation of the AT43USB380 USB Host/Function/OTG Processor.

#### 1.1 Development Kit Packages and Features

The AT43DK380 Development Kit comes in the following packages:

- AT43DK380-BD1 AT43USB380 Development Kit bundled set 1:

- AT43DK380 Main Development Platform with pre-programmed flash set for the PDC1 32-bit ARM7TDMI<sup>®</sup> Processor

- AT43DK380-PDC1 32-bit ARM7TDMI Processor Daughter Card

- Pre-compiled ANSI-C compliant USB Firmware Libraries including USB Host Stack and Device Class Drivers for the PDC1 32-bit ARM7TDMI Processor

- USB Clinic In-Circuit Emulation tool

- AT43DK380-BD2 AT43USB380 Development Kit bundled set 2:

- AT43DK380 Main Development Platform with pre-programmed flash set for the PDC2 AT91R40008 16-bit ARM7TDMI Processor

- AT43DK380-PDC2 AT91R40008 16-bit ARM7TDMI Processor Daughter Card

- Pre-compiled ANSI-C compliant USB Firmware Libraries including USB Host Stack and Device Class Drivers for the PDC2 AT91R40008 16-bit ARM7TDMI Processor

- USB Clinic In-Circuit Emulation tool

- AT43DK380-PDC1 32-bit ARM7TDMI Processor Daughter Card set:

- AT43DK380-PDC1 32-bit ARM7TDMI Processor Daughter Card

- Pre-programmed flash set for the PDC1 32-bit ARM7TDMI Processor

- Pre-compiled ANSI-C compliant USB Firmware Libraries including USB Host Stack and Device Class Drivers for the PDC1 32-bit ARM7TDMI Processor

- USB Clinic In-Circuit Emulation tool

- AT43DK380-PDC2 Atmel AT91R40008 16-bit ARM7TDMI Processor Daughter Card set:

- AT43DK380-PDC2 AT91R40008 16-bit ARM7TDMI Processor Daughter Card

- Pre-programmed flash set for the PDC2 AT91R40008 16-bit ARM7TDMI Processor

- Pre-compiled ANSI-C compliant USB Firmware Libraries including USB Host Stack and Device Class Drivers for the PDC2 AT91R40008 16-bit ARM7TDMI Processor

- USB Clinic In-Circuit Emulation tool

A complete development kit contains a Main Development Platform and a Daughter Card. The pre-programmed flash set and the software tools are functional only for the complete development kit. We recommend purchasing a bundled set for initial development.

The AT43DK380 Main Development Platform consists of the following features:

- AT43USB380 USB Host/Function/OTG Processor

- 1M Bytes Flash ROM

- 2M Bytes Static RAM

- USB MINI A/B ports

- 4-Ports USB Hub

- OTG Interface Charge Pump

- RS-232 Serial Port

- 8/16/32-bit System Processor Interface

- 64 I/Os CPLD

- EEPROM Connector

- Reset buttOn

- Power Indicator LEDs

- In-System Firmware Programming Capability

Please register at http://www.atmel.com/products/usb/forms/softwareg.asp to access and be informed of the latest up-to-date information on new USB software, documentation releases and tool upgrades.

### **Section 2**

### **Getting Started**

### 2.1 Electrostatic Warning

The AT43DK380 Development Platform is shipped in protective anti-static packaging. The board must not be subjected to high electrostatic potentials. A grounding strap or similar protective device should be worn when handling the board. Avoid touching the component pins or any other metallic elements.

#### 2.2 Unpacking the System

The bundled development kit is supplied with the following:

- AT43DK380 Main Development Platform

- AT43DK380 Processor Daughter Card

- Female-female DB9 Null-modem Cable

- 2m Fully Rated USB Cable

- 5V regulated power supply

- Atmel USB CD-ROM with Software and Documentation

- CD-ROM of Atmel Products

Please contact your local Atmel distribution or E-mail usb@atmel.com if any of the aforementioned items is missing from the package.

### 2.3 System Requirements

The minimum hardware and software requirements are:

- 486 Processor (Pentium® is recommended)

- 128 MB RAM

- 10 MB Free Hard Disk Space

- Windows® 98/2000/ME/XP

- RS-232 Port (COM port)

In order to use the AT43DK380 Development Platform with the tools provided, one of the Processor Daughter Cards (PDC) needs to be properly configured and plugged in. The hardware test will only work if the PDC is plugged in.

### 2.4 Connecting the Hardware

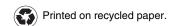

Atmel has taken great care in creating a reliable demonstration kit for its customers. In order to ensure proper operation, the supplied components in the kit must be used in the setup as shown in Figure 2-1. Atmel does NOT recommend substitution of these components.

Figure 2-1. Connection to the AT43DK380

Connect the AT43DK380 Evaluation Board as follows:

- 1. Connect the serial cable from J5 on the evaluation board to a COM port on the PC.

- 2. Connect the AC input connector of the power supply to an AC wall outlet (110 VAC).

- 3. Connect the DC output connector of the power supply to J1 on the evaluation board.

# 2.5 Installing AT43DK380 and Starting Up the USB Clinic

To install the AT43DK380:

- Insert the "Atmel AT43DK380" CD into the CD-ROM drive of the PC or notebook, double-click on the MSI file and follow the instructions.

- 2. After installation, the AT43USB380 documents, firmware, and software should be installed on the C:\Program Files\ATMEL USB\AT43DK380\_Date, if the default installation directory is used. One of the software programs installed is the USB Clinic. It is an integrated diagnostic and debugging tool that provides communication between the AT43DK380 and the PC. Please refer to Section 4 of this User's Guide for detailed description of this tool.

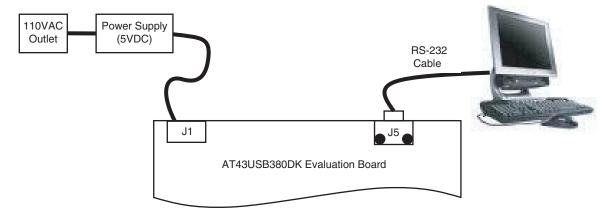

- 3. To invoke the USB Clinic program from desktop go to **Start > Programs > Atmel USB Clinic > Atmel USB Clinic**. The screen in Figure 2-2-will appear.

Figure 2-2. USB Clinic - Main Menu

### 2.6 Testing the Hardware

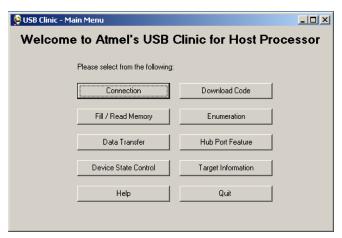

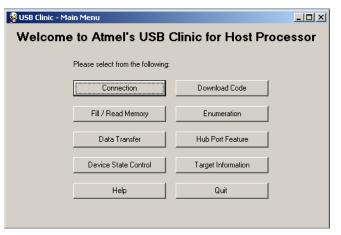

From the USB Clinic **Main Menu** click **Connection** (Figure 2-3 and Figure 2-4 will appear). The **Connection** button allows testing of the RS-232 serial port and the AT43DK380 Development Platform connection. Prior to going to the **Connection** menu, please make sure that the AT43DK380 is physically connected to the PC with the supplied serial cable or any standard serial cable.

Figure 2-3. USB Clinic - Connection

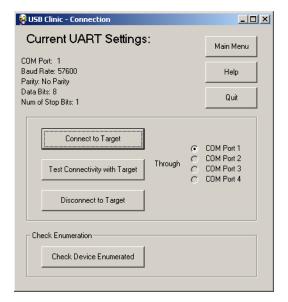

Figure 2-4. COM Port Availability

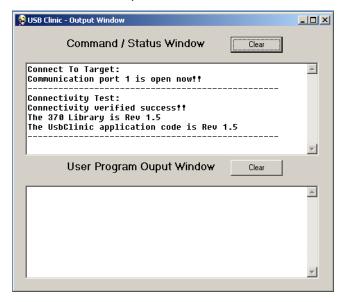

The USB Clinic automatically detects and displays the availability of COM ports from COM1 to COM4 in the **Connection** window. Users can use any available COM port by simply selecting the desired COM port and then clicking the **Connect to Target** button to open the selected COM port. To verify connectivity between the selected COM port and the AT43DK380 Development Platform, click on **Test Connectivity with Target** and look for *Connection verified* in the **Output Window** (see Figure 2-5). The **Test Connectivity with Target** also checks the AT43DK380 firmware revision to see if it supports the current USB Clinic version.

Figure 2-5. Connection Verified Output Window

Once the connection is established, USB Clinic is ready for use. Please refer to Section 4 for more details.

### **Section 3**

### **Hardware Description**

The AT43DK380 Development Platform comes pre-configured as a USB Host in Flash (Standalone) mode. Alternative settings are available through jumper configurations. This section gives the basic description about the hardware components and the jumper settings of the AT43DK380 Development Platforms.

Section 9 contains the complete AT43DK380 schematics and bill of materials.

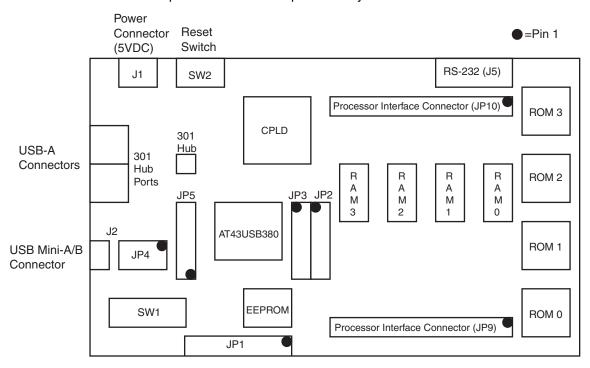

# 3.1 Description of the Main Development Platform

The AT43DK380 Main Development Platform consists of the AT43USB380 Host/Function/OTG processor, 1 Mbytes of Flash ROM, 2 Mbytes of SRAM, 4 port USB Hub, USB type MINI-A/B port, RS-232 serial port, and pre-programmed CPLD and glue logic for configurable bus width interface. The AT43USB380 connects to the system processor through the configurable bus width interface connectors. The RS-232 port provides access to the system processor and the AT43USB380, and the In-System Programming to SRAM.

Figure 3-1. AT43USB380 Main Development Platform Components Layout

## 3.1.1 AT43DK380 Processor Interface Connector

The AT43DK380 Main Development Platform provides a generic processor interface to allow a wide variety of processors to communicate with the on-board RAM, ROM and the AT43USB380 USB Host. The pin assignments and descriptions for the connectors are as follows:

Table 3-1. J9: Processor Interface Connector 1

| Pin #        | Pin Name | Signal Source | Pin Description |

|--------------|----------|---------------|-----------------|

| 1, 2, 49, 50 | VCC_3.3  |               | Power: 3.3 VDC  |

| 3            | D0       | Bi-Direction  | Data Bit 0      |

| 4            | D1       | Bi-Direction  | Data Bit 1      |

| 5            | D2       | Bi-Direction  | Data Bit 2      |

| 6            | D3       | Bi-Direction  | Data Bit 3      |

| 7            | D4       | Bi-Direction  | Data Bit 4      |

| 8            | D5       | Bi-Direction  | Data Bit 5      |

| 9            | D6       | Bi-Direction  | Data Bit 6      |

| 10           | D7       | Bi-Direction  | Data Bit 7      |

| 13           | D8       | Bi-Direction  | Data Bit 8      |

| 14           | D9       | Bi-Direction  | Data Bit 9      |

| 15           | D10      | Bi-Direction  | Data Bit10      |

| 16           | D11      | Bi-Direction  | Data Bit 11     |

| 17           | D12      | Bi-Direction  | Data Bit 12     |

| 18           | D13      | Bi-Direction  | Data Bit 13     |

Table 3-1. J9: Processor Interface Connector 1

| Pin #                             | Pin Name | Signal Source                                     | Pin Description                              |

|-----------------------------------|----------|---------------------------------------------------|----------------------------------------------|

| 19                                | D14      | Bi-Direction                                      | Data Bit 14                                  |

| 20                                | D15      | Bi-Direction                                      | Data Bit 15                                  |

| 23                                | D16      | Bi-Direction                                      | Data Bit 16                                  |

| 24                                | D17      | Bi-Direction                                      | Data Bit 17                                  |

| 25                                | D18      | Bi-Direction                                      | Data Bit 18                                  |

| 26                                | D19      | Bi-Direction                                      | Data Bit 19                                  |

| 27                                | D20      | Bi-Direction                                      | Data Bit 20                                  |

| 28                                | D21      | Bi-Direction                                      | Data Bit 21                                  |

| 29                                | D22      | Bi-Direction                                      | Data Bit 22                                  |

| 30                                | D23      | Bi-Direction                                      | Data Bit 23                                  |

| 33                                | D24      | Bi-Direction                                      | Data Bit 24                                  |

| 34                                | D25      | Bi-Direction                                      | Data Bit 25                                  |

| 35                                | D26      | Bi-Direction                                      | Data Bit 26                                  |

| 36                                | D27      | Bi-Direction                                      | Data Bit 27                                  |

| 37                                | D28      | Bi-Direction                                      | Data Bit 28                                  |

| 38                                | D29      | Bi-Direction                                      | Data Bit 29                                  |

| 39                                | D30      | Bi-Direction                                      | Data Bit 30                                  |

| 40                                | D31      | Bi-Direction                                      | Data Bit 31                                  |

| 43                                | NDACK    | System Processor                                  | DMA Acknowledge                              |

| 44                                | NDREQ    | AT43USB380                                        | DMA Request                                  |

| 45                                | NWAIT    | AT43USB380                                        |                                              |

| 46                                | INTREQ   | AT43USB380                                        | Interrupt Request                            |

| 47                                | NRESET   | AT43DK380<br>(Main Development Platform and PDCs) | System Reset, Active Low                     |

| 48                                | NWAKEUP  | System Processor                                  | AT43USB380 Wake-Up request from Suspend Mode |

| 11, 12, 21, 22,<br>31, 32, 41, 42 | GND      |                                                   | Power: Ground                                |

Table 3-2. J10: Processor Interface Connector 2

| 1, 2, 49, 50         VCC_3.3         Power: 3.3 VDC           3         A0         System Processor         Address Bit 0           4         A1         System Processor         Address Bit 1           5         A2         System Processor         Address Bit 2           6         A3         System Processor         Address Bit 3           7         A4         System Processor         Address Bit 4           8         A5         System Processor         Address Bit 5           9         A6         System Processor         Address Bit 6           10         A7         System Processor         Address Bit 7           11         A8         System Processor         Address Bit 8           12         A9         System Processor         Address Bit 9           15         A10         System Processor         Address Bit 10           16         A11         System Processor         Address Bit 11           17         A12         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 12           19         A14         System Processor         Address Bit 16           20         A15         System Proces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin #        | Pin Name | Signal Source    | Pin Description                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|------------------|--------------------------------|

| 4         A1         System Processor         Address Bit 1           5         A2         System Processor         Address Bit 2           6         A3         System Processor         Address Bit 3           7         A4         System Processor         Address Bit 4           8         A5         System Processor         Address Bit 5           9         A6         System Processor         Address Bit 6           10         A7         System Processor         Address Bit 7           11         A8         System Processor         Address Bit 8           12         A9         System Processor         Address Bit 9           15         A10         System Processor         Address Bit 10           16         A11         System Processor         Address Bit 11           17         A12         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 16           21         A16         System Processor         Address Bit 16           22         A17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1, 2, 49, 50 | VCC_3.3  |                  | Power: 3.3 VDC                 |

| 5         A2         System Processor         Address Bit 2           6         A3         System Processor         Address Bit 3           7         A4         System Processor         Address Bit 4           8         A5         System Processor         Address Bit 5           9         A6         System Processor         Address Bit 6           10         A7         System Processor         Address Bit 7           11         A8         System Processor         Address Bit 8           12         A9         System Processor         Address Bit 9           15         A10         System Processor         Address Bit 10           16         A11         System Processor         Address Bit 11           17         A12         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3            | A0       | System Processor | Address Bit 0                  |

| 6         A3         System Processor         Address Bit 3           7         A4         System Processor         Address Bit 4           8         A5         System Processor         Address Bit 5           9         A6         System Processor         Address Bit 6           10         A7         System Processor         Address Bit 7           11         A8         System Processor         Address Bit 8           12         A9         System Processor         Address Bit 9           15         A10         System Processor         Address Bit 10           16         A11         System Processor         Address Bit 11           17         A12         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 18           24         A19 </td <td>4</td> <td>A1</td> <td>System Processor</td> <td>Address Bit 1</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4            | A1       | System Processor | Address Bit 1                  |

| 7         A4         System Processor         Address Bit 4           8         A5         System Processor         Address Bit 5           9         A6         System Processor         Address Bit 6           10         A7         System Processor         Address Bit 7           11         A8         System Processor         Address Bit 8           12         A9         System Processor         Address Bit 9           15         A10         System Processor         Address Bit 10           16         A11         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 16           20         A15         System Processor         Address Bit 16           21         A16         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 18           24         A19         System Processor         Address Bit 20           25         A20         System Processor         Address Bit 20           26         EX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5            | A2       | System Processor | Address Bit 2                  |

| 8         A5         System Processor         Address Bit 5           9         A6         System Processor         Address Bit 6           10         A7         System Processor         Address Bit 7           11         A8         System Processor         Address Bit 8           12         A9         System Processor         Address Bit 9           15         A10         System Processor         Address Bit 10           16         A11         System Processor         Address Bit 11           17         A12         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 18           24         A19         System Processor         Address Bit 19           25         A20         System Processor         Address Bit 20           26 <td< td=""><td>6</td><td>A3</td><td>System Processor</td><td>Address Bit 3</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6            | A3       | System Processor | Address Bit 3                  |

| 9         A6         System Processor         Address Bit 6           10         A7         System Processor         Address Bit 7           11         A8         System Processor         Address Bit 8           12         A9         System Processor         Address Bit 9           15         A10         System Processor         Address Bit 10           16         A11         System Processor         Address Bit 11           17         A12         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 18           24         A19         System Processor         Address Bit 20           25         A20         System Processor         Address Bit 20           26         EXTRA1         CPLD         Address Bit 20           26         EXTRA1         CPLD         Address Bit 19           30         EXTRA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7            | A4       | System Processor | Address Bit 4                  |

| 10         A7         System Processor         Address Bit 7           11         A8         System Processor         Address Bit 8           12         A9         System Processor         Address Bit 9           15         A10         System Processor         Address Bit 10           16         A11         System Processor         Address Bit 11           17         A12         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 19           24         A19         System Processor         Address Bit 19           25         A20         System Processor         Address Bit 20           26         EXTRA1         CPLD         Additional signal to/from CPLD           30         EXTRA2         CPLD         Unused signal to/from CPLD           31<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8            | A5       | System Processor | Address Bit 5                  |

| 11         A8         System Processor         Address Bit 8           12         A9         System Processor         Address Bit 9           15         A10         System Processor         Address Bit 10           16         A11         System Processor         Address Bit 11           17         A12         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 19           24         A19         System Processor         Address Bit 20           26         EXTRA1         CPLD         Additional signal to/from CPLD           29         NRD         System Processor         Read Enable. Active Low           30         EXTRA2         CPLD         Unused signal to/from CPLD           31         nWBE0         System Processor         Write Byte 0. Active Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9            | A6       | System Processor | Address Bit 6                  |

| 12         A9         System Processor         Address Bit 9           15         A10         System Processor         Address Bit 10           16         A11         System Processor         Address Bit 11           17         A12         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 19           24         A19         System Processor         Address Bit 20           26         EXTRA1         CPLD         Additional signal to/from CPLD           29         NRD         System Processor         Read Enable. Active Low           30         EXTRA2         CPLD         Unused signal to/from CPLD           31         nWBE0         System Processor         Write Byte 1. Active Low           32         nWBE1         System Processor         Write Byte 2. Active Low <td>10</td> <td>A7</td> <td>System Processor</td> <td>Address Bit 7</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10           | A7       | System Processor | Address Bit 7                  |

| 15         A10         System Processor         Address Bit 10           16         A11         System Processor         Address Bit 11           17         A12         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 18           24         A19         System Processor         Address Bit 19           25         A20         System Processor         Address Bit 20           26         EXTRA1         CPLD         Additional signal to/from CPLD           29         NRD         System Processor         Read Enable. Active Low           30         EXTRA2         CPLD         Unused signal to/from CPLD           31         nWBE0         System Processor         Write Byte 0. Active Low           32         nWBE1         System Processor         Write Byte 2. Active Low<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11           | A8       | System Processor | Address Bit 8                  |

| 16         A11         System Processor         Address Bit 11           17         A12         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 18           24         A19         System Processor         Address Bit 19           25         A20         System Processor         Address Bit 20           26         EXTRA1         CPLD         Additional signal to/from CPLD           29         NRD         System Processor         Read Enable. Active Low           30         EXTRA2         CPLD         Unused signal to/from CPLD           31         nWBE0         System Processor         Write Byte 0. Active Low           32         nWBE1         System Processor         Write Byte 2. Active Low           34         nWBE3         System Processor         Chip Select 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12           | A9       | System Processor | Address Bit 9                  |

| 17         A12         System Processor         Address Bit 12           18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 18           24         A19         System Processor         Address Bit 20           25         A20         System Processor         Address Bit 20           26         EXTRA1         CPLD         Additional signal to/from CPLD           29         NRD         System Processor         Read Enable. Active Low           30         EXTRA2         CPLD         Unused signal to/from CPLD           31         nWBE0         System Processor         Write Byte 0. Active Low           32         nWBE1         System Processor         Write Byte 2. Active Low           33         nWBE2         System Processor         Write Byte 3. Active Low           34         nWBE3         System Processor         C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15           | A10      | System Processor | Address Bit 10                 |

| 18         A13         System Processor         Address Bit 13           19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 18           24         A19         System Processor         Address Bit 20           25         A20         System Processor         Address Bit 20           26         EXTRA1         CPLD         Additional signal to/from CPLD           29         NRD         System Processor         Read Enable. Active Low           30         EXTRA2         CPLD         Unused signal to/from CPLD           31         nWBE0         System Processor         Write Byte 0. Active Low           32         nWBE1         System Processor         Write Byte 2. Active Low           34         nWBE3         System Processor         Write Byte 3. Active Low           35         nCS0         System Processor         Chip Select 0. Active Low           36         nCS1         System Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16           | A11      | System Processor | Address Bit 11                 |

| 19         A14         System Processor         Address Bit 14           20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 18           24         A19         System Processor         Address Bit 19           25         A20         System Processor         Address Bit 20           26         EXTRA1         CPLD         Additional signal to/from CPLD           29         NRD         System Processor         Read Enable. Active Low           30         EXTRA2         CPLD         Unused signal to/from CPLD           31         nWBE0         System Processor         Write Byte 0. Active Low           32         nWBE1         System Processor         Write Byte 2. Active Low           33         nWBE2         System Processor         Write Byte 3. Active Low           34         nWBE3         System Processor         Chip Select 0. Active Low           36         nCS1         System Processor         Chip Select 1. Active Low           37         nCS2         System Proc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17           | A12      | System Processor | Address Bit 12                 |

| 20         A15         System Processor         Address Bit 15           21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 18           24         A19         System Processor         Address Bit 20           25         A20         System Processor         Additional signal to/from CPLD           29         NRD         System Processor         Read Enable. Active Low           30         EXTRA2         CPLD         Unused signal to/from CPLD           31         nWBE0         System Processor         Write Byte 0. Active Low           32         nWBE1         System Processor         Write Byte 1. Active Low           33         nWBE2         System Processor         Write Byte 2. Active Low           34         nWBE3         System Processor         Write Byte 3. Active Low           35         nCS0         System Processor         Chip Select 0. Active Low           36         nCS1         System Processor         Chip Select 2. Active Low           37         nCS2         System Processor         Chip Select 2. Active Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18           | A13      | System Processor | Address Bit 13                 |

| 21         A16         System Processor         Address Bit 16           22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 18           24         A19         System Processor         Address Bit 19           25         A20         System Processor         Address Bit 20           26         EXTRA1         CPLD         Additional signal to/from CPLD           29         NRD         System Processor         Read Enable. Active Low           30         EXTRA2         CPLD         Unused signal to/from CPLD           31         nWBE0         System Processor         Write Byte 0. Active Low           32         nWBE1         System Processor         Write Byte 1. Active Low           33         nWBE2         System Processor         Write Byte 2. Active Low           34         nWBE3         System Processor         Write Byte 3. Active Low           35         nCS0         System Processor         Chip Select 0. Active Low           36         nCS1         System Processor         Chip Select 1. Active Low           37         nCS2         System Processor         Chip Select 2. Active Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19           | A14      | System Processor | Address Bit 14                 |

| 22         A17         System Processor         Address Bit 17           23         A18         System Processor         Address Bit 18           24         A19         System Processor         Address Bit 19           25         A20         System Processor         Address Bit 20           26         EXTRA1         CPLD         Additional signal to/from CPLD           29         NRD         System Processor         Read Enable. Active Low           30         EXTRA2         CPLD         Unused signal to/from CPLD           31         nWBE0         System Processor         Write Byte 0. Active Low           32         nWBE1         System Processor         Write Byte 1. Active Low           33         nWBE2         System Processor         Write Byte 3. Active Low           34         nWBE3         System Processor         Chip Select 0. Active Low           35         nCS0         System Processor         Chip Select 1. Active Low           36         nCS1         System Processor         Chip Select 2. Active Low           37         nCS2         System Processor         Chip Select 2. Active Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20           | A15      | System Processor | Address Bit 15                 |

| 23         A18         System Processor         Address Bit 18           24         A19         System Processor         Address Bit 19           25         A20         System Processor         Address Bit 20           26         EXTRA1         CPLD         Additional signal to/from CPLD           29         NRD         System Processor         Read Enable. Active Low           30         EXTRA2         CPLD         Unused signal to/from CPLD           31         nWBE0         System Processor         Write Byte 0. Active Low           32         nWBE1         System Processor         Write Byte 1. Active Low           33         nWBE2         System Processor         Write Byte 3. Active Low           34         nWBE3         System Processor         Chip Select 0. Active Low           35         nCS0         System Processor         Chip Select 1. Active Low           36         nCS1         System Processor         Chip Select 2. Active Low           37         nCS2         System Processor         Chip Select 2. Active Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21           | A16      | System Processor | Address Bit 16                 |

| 24         A19         System Processor         Address Bit 19           25         A20         System Processor         Address Bit 20           26         EXTRA1         CPLD         Additional signal to/from CPLD           29         NRD         System Processor         Read Enable. Active Low           30         EXTRA2         CPLD         Unused signal to/from CPLD           31         nWBE0         System Processor         Write Byte 0. Active Low           32         nWBE1         System Processor         Write Byte 1. Active Low           33         nWBE2         System Processor         Write Byte 2. Active Low           34         nWBE3         System Processor         Chip Select 0. Active Low           35         nCS0         System Processor         Chip Select 1. Active Low           36         nCS1         System Processor         Chip Select 2. Active Low           37         nCS2         System Processor         Chip Select 2. Active Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22           | A17      | System Processor | Address Bit 17                 |

| Address Bit 20  EXTRA1 CPLD Additional signal to/from CPLD  NRD System Processor Read Enable. Active Low  EXTRA2 CPLD Unused signal to/from CPLD  NWBE0 System Processor Write Byte 0. Active Low  NWBE1 System Processor Write Byte 1. Active Low  NWBE2 System Processor Write Byte 2. Active Low  NWBE3 System Processor Write Byte 3. Active Low  NWBE3 System Processor Chip Select 0. Active Low  Chip Select 1. Active Low  Chip Select 1. Active Low  Chip Select 2. Active Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23           | A18      | System Processor | Address Bit 18                 |

| 26 EXTRA1 CPLD Additional signal to/from CPLD  29 NRD System Processor Read Enable. Active Low  30 EXTRA2 CPLD Unused signal to/from CPLD  31 nWBE0 System Processor Write Byte 0. Active Low  32 nWBE1 System Processor Write Byte 1. Active Low  33 nWBE2 System Processor Write Byte 2. Active Low  34 nWBE3 System Processor Write Byte 3. Active Low  35 nCS0 System Processor Chip Select 0. Active Low  36 nCS1 System Processor Chip Select 1. Active Low  37 nCS2 System Processor Chip Select 2. Active Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24           | A19      | System Processor | Address Bit 19                 |

| NRD System Processor Read Enable. Active Low  EXTRA2 CPLD Unused signal to/from CPLD  nWBE0 System Processor Write Byte 0. Active Low  nWBE1 System Processor Write Byte 1. Active Low  NWBE2 System Processor Write Byte 2. Active Low  NWBE3 System Processor Write Byte 3. Active Low  NWBE3 System Processor Chip Select 0. Active Low  Chip Select 1. Active Low  NCS1 System Processor Chip Select 2. Active Low  Chip Select 2. Active Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25           | A20      | System Processor | Address Bit 20                 |

| 30 EXTRA2 CPLD Unused signal to/from CPLD 31 nWBE0 System Processor Write Byte 0. Active Low 32 nWBE1 System Processor Write Byte 1. Active Low 33 nWBE2 System Processor Write Byte 2. Active Low 34 nWBE3 System Processor Write Byte 3. Active Low 35 nCS0 System Processor Chip Select 0. Active Low 36 nCS1 System Processor Chip Select 1. Active Low 37 nCS2 System Processor Chip Select 2. Active Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26           | EXTRA1   | CPLD             | Additional signal to/from CPLD |

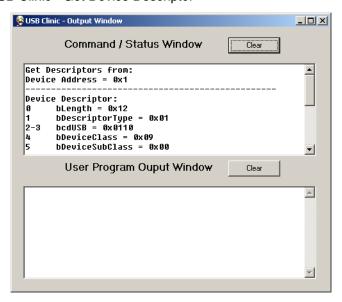

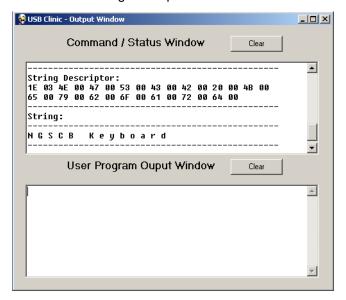

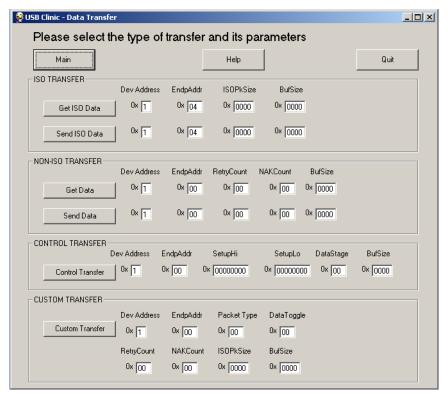

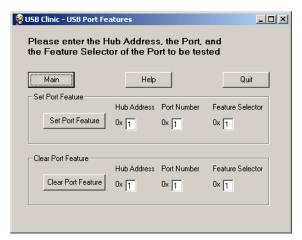

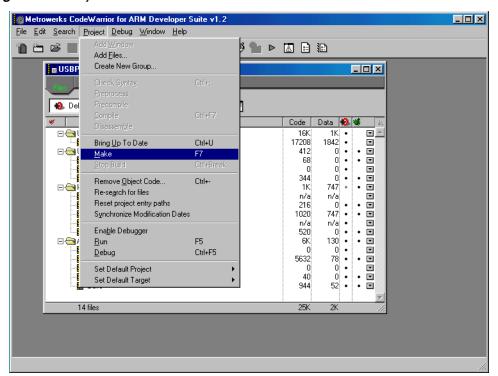

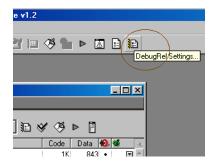

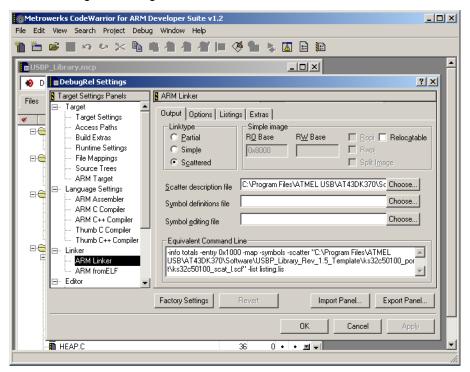

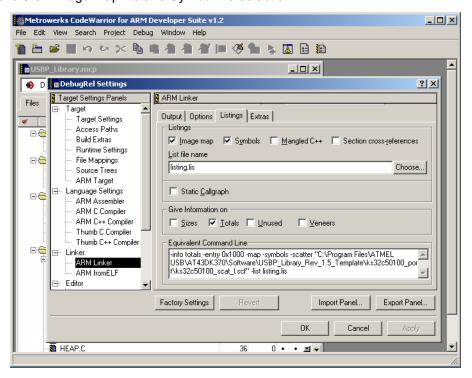

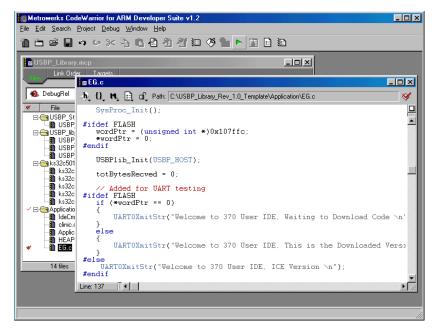

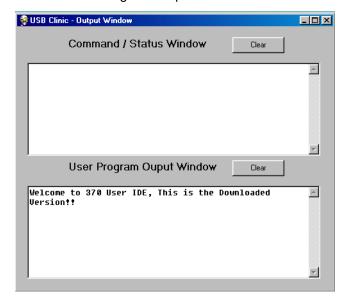

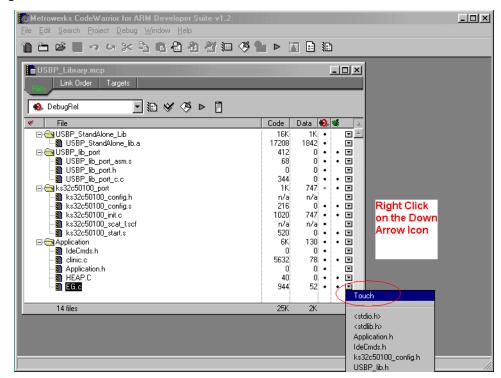

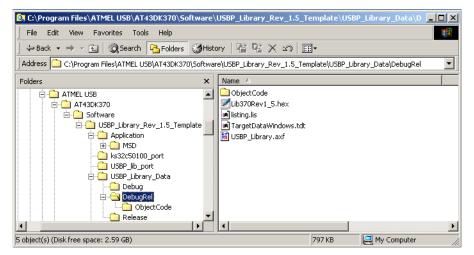

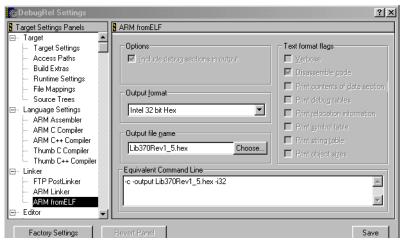

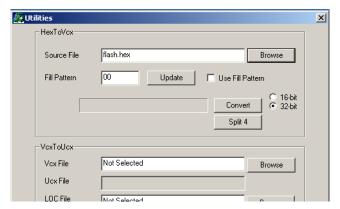

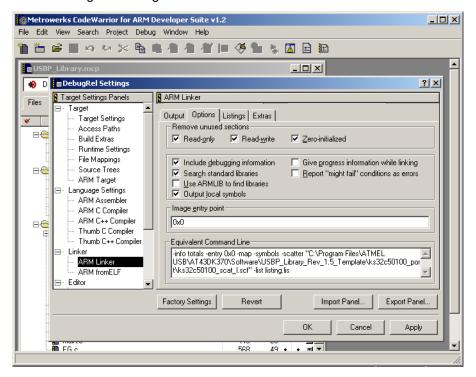

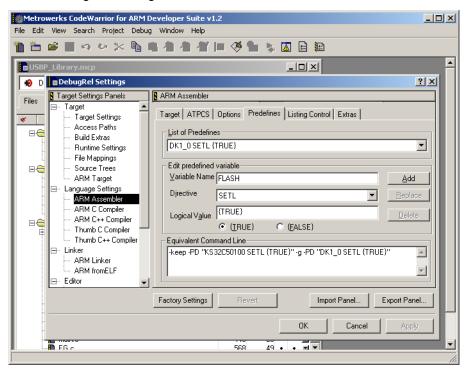

| nWBE0 System Processor Write Byte 0. Active Low  NWBE1 System Processor Write Byte 1. Active Low  NWBE2 System Processor Write Byte 2. Active Low  NWBE3 System Processor Write Byte 3. Active Low  NCS0 System Processor Chip Select 0. Active Low  Chip Select 1. Active Low  NCS1 System Processor Chip Select 1. Active Low  Chip Select 2. Active Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29           | NRD      | System Processor | Read Enable. Active Low        |